(一) 画好原理图很多工程师都觉得layout工作更重要一些,原理图就是为了生成网表方便PCB做检查用的。其实,在后续电路调试过程中原理图的作用会更大一些。无论是查找问题还是和同事交流,还是原理图更直观更方便。另外养成在原理图中做标注的习惯,把各部分电路在layout的时候要注意到的问题标注在原理图上,对自己或者对别人都是一个很好的提醒。层次化原理图,把不同功能不同模块的电路分成不同的页,这样无论是读图还是以后重复使用都能明显的减少工作量。使用成熟的设计总是要比设计新电路的风险小。每次看到把所有电路都放在一张图纸上,一片密密麻麻的器件,脑袋就能大一圈。(二) 好好进行电路布局心急的工程师画完原理图,把网表导入PCB后就迫不及待的把器件放好,开始拉线。其实一个好的PCB布局能让你后面的拉线工作变得简单,让你的PCB工作的更好。每一块板子都会有一个信号路径,PCB布局也应该尽量遵循这个信号路径,让信号在板子上可以顺畅的传输,人们都不喜欢走迷宫,信号也一样。如果原理图是按照模块设计的,PCB也一样可以。按照不同的功能模块可以把板子划分为若干区域。模拟数字分开,电源信号分开,发热器件和易感器件分开,体积较大的器件不要太靠近板边,注意射频信号的屏蔽等等……多花一分的时间去优化PCB的布局,就能在拉线的时候节省更多的时间。

尤其在使用高速数据网络时,拦截大量信息所需要的时间显著低于拦截低速数据传输所需要的时间。数据双绞线中的绞合线对在低频下可以靠自身的绞合来抵抗外来干扰及线对之间的串音,但在高频情况下(尤其在频率超过250MHz以上时),仅靠线对绞合已无法达到抗干扰的目的,只有屏蔽才能够抵抗外界干扰。电缆屏蔽层的作用就像一个法拉第护罩,干扰信号会进入到屏蔽层里,但却进入不到导体中。因此,数据传输可以无故障运行。由于屏蔽电缆比非屏蔽电缆具有较低的辐射散发,因而防止了网络传输被拦截。屏蔽网络(屏蔽的电缆及元器件)能够显著减小进入到周围环境中而可能被拦截的电磁能辐射等级。不同干扰场的屏蔽选择干扰场主要有电磁干扰及射频干扰两种。电磁干扰(EMI)主要是低频干扰,马达、荧光灯以及电源线是通常的电磁干扰源。射频干扰(RFI)是指无线频率干扰,主要是高频干扰。无线电、电视转播、雷达及其他无线通讯是通常的射频干扰源。对于抵抗电磁干扰,选择编织屏蔽最为有效,因其具有较低的临界电阻;对于射频干扰,箔层屏蔽最有效,因编织屏蔽依赖于波长的变化,它所产生的缝隙使得高频信号可自由进出导体;而对于高低频混合的干扰场,则要采用具有宽带覆盖功能的箔层加编织网的组合屏蔽方式。通常,网状屏蔽覆盖率越高,屏蔽效果就越好。

覆铜时铜和导线之间的间距要改变覆铜时铜和导线以及焊盘之间的间距,方法如下:设计—规则—Electrical—clearance,点右键建立“新规则”,出现clearance_1,在clearance_1规则中“第Y个对象匹配哪里”栏中选中“高级(查询)”,在右边的“全查询”栏中输入(InPoly),最后点“应用”结束。如果输入不对,选则“所有”后再选“高级(查询)”。pcb中放置某个器件时无论如何都报错在pcb中放置某个元件时,无论如何都报错,解决办法是将规则里的线间距改小。如何选中所有连在一起的线或同一网络的线按住“Ctrl”左键单击想要选中的网络线即可。无意中按出来个放大镜在无意中按出来个放大镜,用“SHIFT+M”取消或者选菜单项“工具”——“优先选项”——“pcb Editor”——“Board Insight Lens”,勾选或取消“可视”即可。

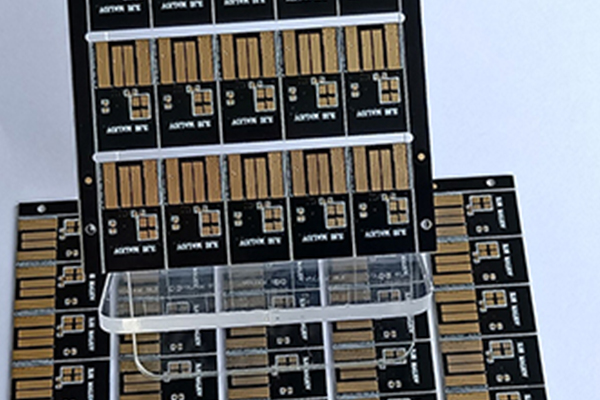

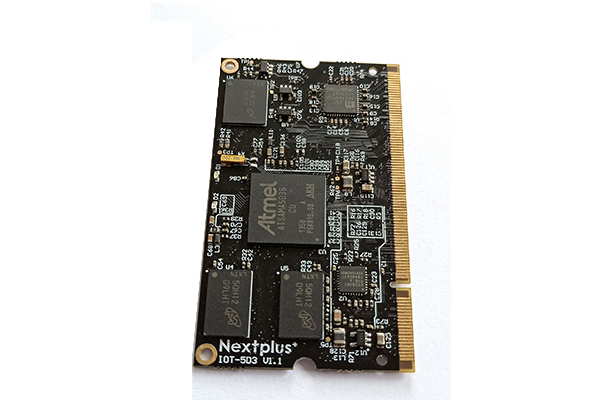

重庆厂家PCB电路板1)专门用于探测的测试焊盘的直径应该不小于0.9mm 。2) 测试焊盘周围的空间应大于0.6mm 而小于5mm 。PCB电路板加工厂如果元器件的高度大于6. 7mm,那么测试焊盘应置于该元器件5mm 以外。3) 在距离印制电路板边缘3mm 以内不要放置任何元器件或测试焊盘。4) 测试焊盘应放在一个网格中2.5mm孔的中心。如果有可能,允许使用标准探针和一个更可靠的固定装置。5) 不要依靠连接器指针的边缘来进行焊盘测试。测试探针很容易损坏镀金指针。6) 避免镀通孔-印制电路板两边的探查。把测试顶端通过孔放到印制电路板的非元器件/焊接面上。