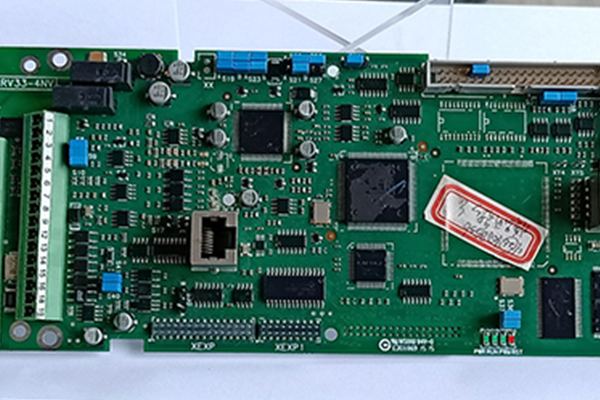

1. 如果是人工焊接,要养成好的习惯,首先,焊接前要目视检查一遍PCB板,并用万用表检查关键电路(特别是电源与地)是否短路;其次,每次焊接完一个芯片就用万用表测一下电源和地是否短路;此外,焊接时不要乱甩烙铁,如果把焊锡甩到芯片的焊脚上(特别是表贴元件),就不容易查到。2. 在计算机上打开PCB图,点亮短路的网络,看什么地方离的最近,最容易被连到一块。特别要注意IC内部短路。3. 发现有短路现象。拿一块板来割线(特别适合单/双层板),割线后将每部分功能块分别通电,一部分一部分排除。4. 使用短路定位分析仪,如:新加坡PROTEQ CB2000短路追踪仪,香港灵智科技QT50短路追踪仪,英国POLAR ToneOhm950多层板路短路探测仪等等。5. 如果有BGA芯片,由于所有焊点被芯片覆盖看不见,而且又是多层板(4层以上),因此最好在设计时将每个芯片的电源分割开,用磁珠或0欧电阻连接,这样出现电源与地短路时,断开磁珠检测,很容易定位到某一芯片。由于BGA的焊接难度大,如果不是机器自动焊接,稍不注意就会把相邻的电源与地两个焊球短路。

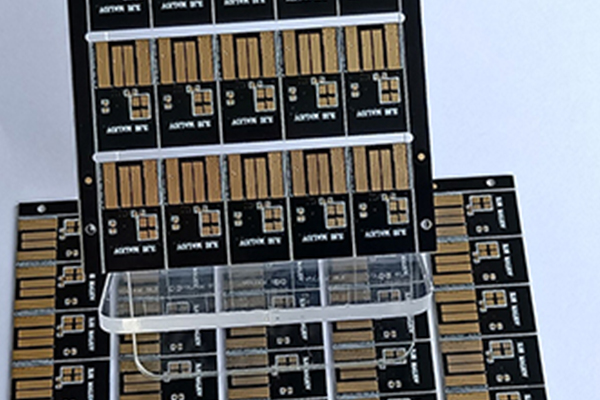

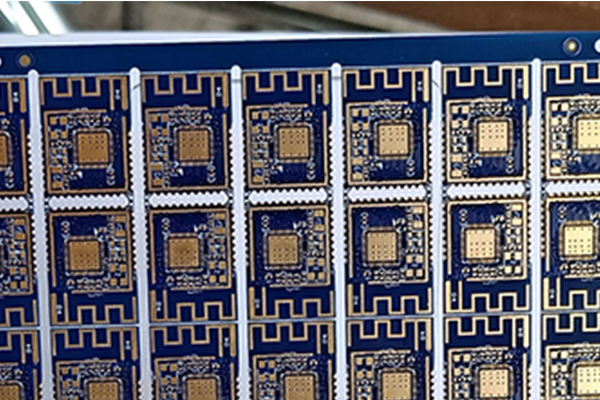

一、沉金板与镀金板的区别二、为什么要用镀金板随着IC 的集成度越来越高,IC脚也越多越密。而垂直喷锡工艺很难将成细的焊盘吹平整,这就给SMT的贴装带来了难度;另外喷锡板的待用寿命(shelf life)很短。而镀金板正好解决了这些问题: 1对于表面贴装工艺,尤其对于0603及0402 超小型表贴,因为焊盘平整度直接关系到锡膏印制工序的质量,对后面的再流焊接质量起到决定性影响,所以,整板镀金在高密度和超小型表贴工艺中时常见到。2在试制阶段,受元件采购等因素的影响往往不是板子来了马上就焊,而是经常要等上几个星期甚至个把月才用,镀金板的待用寿命(shelf life)比铅锡合金长很多倍所以大家都乐意采用。再说镀金PCB在度样阶段的成本与铅锡合金板相比相差无几。但随着布线越来越密,线宽、间距已经到了3-4MIL。因此带来了金丝短路的问题:随着信号的频率越来越高,因趋肤效应造成信号在多镀层中传输的情况对信号质量的影响越明显:趋肤效应是指:高频的交流电,电流将趋向集中在导线的表面流动。根据计算,趋肤深度与频率有关:镀金板的其它缺点在沉金板与镀金板的区别表中已列出。

湖北厂家SMT焊接这里主要是说了从PCB设计封装来解析选择元件的技巧。元件的封装包含很多信息,包含元件的尺寸,SMT焊接加工厂特别是引脚的相对位置关系,还有元件的焊盘类型。当然我们根据元件封装选择元件时还有一个要注意的地方是要考虑元件的外形尺寸。引脚位置关系:主要是指我们需要将实际的元件的引脚和PCB元件的封装的尺寸对应起来。我们选择不同的元件,虽然功能相同,但是元件的封装很可能不一样。我们需要保证PCB焊盘尺寸位置正确才能保证元件能正确焊接。焊盘的选择:这个是我们需要考虑的比较多的地方。首先包括焊盘的类型。其类型包括两种,一是电镀通孔,一种是表贴类型。我们需要考虑的因素有器件成本、可用性、器件面积密度和功耗等因数。从制造角度看,表贴器件通常要比通孔器件便宜,而且一般可用性较高。对于我们一般设计来说,我们选择表贴元件,不仅方便手工焊接,而且有利于查错和调试过程中更好的连接焊盘和信号。其次我们还应该注意焊盘的位置。因为不同的位置,就代表元件实际当中不同的位置。我们如果不合理安排焊盘的位置,很有可能就会出现一个区域元件过密,而另外一个区域元件很稀疏的情况,当然情况更糟糕的是由于焊盘位置过近,导致元件之间空隙过小而无法焊接,下面就是我失败的一个例子,我在一个光耦开关旁边开了通孔,但是由于它们的位置过近,导致光耦开关焊接上去以后,通孔无法再放置螺丝了。另外一种情况就是我们要考虑焊盘如何焊接。在实际过程中我们常按一个特定的方向排列焊盘,焊接起来比较方便。元件的外形尺寸:在实际应用当中,一些元件(如有极性电容)可能有高度净空限制,所以我们需要在元件选择过程中加以考虑。我们在最初开始设计时,可以先画一个基本的电路板外框形状,然后放置上一些计划要使用的大型或位置关键元件(如连接器)。这样,就能直观快速地看到(没有布线的)电路板虚拟透视图,并给出相对精确的电路板和元器件的相对定位和元件高度。这将有助于确保PCB经过装配后元件能合适地放进外包装(塑料制品、机箱、机框等)内。当然我们还可以从工具菜单中调用三维预览模式浏览整块电路板。对于元件的选择,除了要依据设计要求外,还要选择正规厂家所生产的产品,这样才能保证实现你的设计目标。

覆铜时铜和导线之间的间距要改变覆铜时铜和导线以及焊盘之间的间距,方法如下:设计—规则—Electrical—clearance,点右键建立“新规则”,出现clearance_1,在clearance_1规则中“第Y个对象匹配哪里”栏中选中“高级(查询)”,在右边的“全查询”栏中输入(InPoly),最后点“应用”结束。如果输入不对,选则“所有”后再选“高级(查询)”。pcb中放置某个器件时无论如何都报错在pcb中放置某个元件时,无论如何都报错,解决办法是将规则里的线间距改小。如何选中所有连在一起的线或同一网络的线按住“Ctrl”左键单击想要选中的网络线即可。无意中按出来个放大镜在无意中按出来个放大镜,用“SHIFT+M”取消或者选菜单项“工具”——“优先选项”——“pcb Editor”——“Board Insight Lens”,勾选或取消“可视”即可。

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%。这有时很难做到,以 FR4板材上微带线的情况为例,我们计算一下。如果线宽8mil,线条和参考平面之间的厚度为4mil,特性阻抗为46.5欧姆。线宽变化到6mil后特性阻抗变成54.2欧姆,阻抗变化率达到了20%。反射信号的幅度必然超标。至于对信号造成多大影响,还和信号上升时间和驱动端到反射点处信号的时延有关。但至少这是一个潜在的问题点。幸运的是这时可以通过阻抗匹配端接解决问题。如果阻抗变化发生两次,例如线宽从8mil变到6mil后,拉出2cm后又变回8mil。那么在2cm长6mil宽线条的两个端点处都会发生反射,一次是阻抗变大,发生正反射,接着阻抗变小,发生负反射。如果两次反射间隔时间足够短,两次反射就有可能相互抵消,从而减小影响。假设传输信号为1V,第Y次正反射有0.2V被反射,1.2V继续向前传输,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假设6mil线长度极短,两次反射几乎同时发生,那么总的反射电压只有0.04V,小于5%这一噪声预算要求。因此,这种反射是否影响信号,有多大影响,和阻抗变化处的时延以及信号上升时间有关。研究及实验表明,只要阻抗变化处的时延小于信号上升时间的20%,反射信号就不会造成问题。如果信号上升时间为1ns,那么阻抗变化处的时延小于0.2ns对应1.2英寸,反射就不会产生问题。也就是说,对于本例情况,6mil宽走线的长度只要小于3cm就不会有问题。