相信对做硬件的工程师,毕业开始进公司时,在设计PCB时,老工程师都会对他说,PCB走线不要走直角,走线一定要短,电容一定要就近摆放等等。但是一开始我们可能都不了解为什么这样做,就凭他们的几句经验对我们来说是远远不够的哦,当然如果你没有注意这些细节问题,今后又犯了,可能又会被他们骂,“都说了多少遍了电容一定要就近摆放,放远了起不到效果等等”,往往经验告诉我们其实那些老工程师也是只有一部分人才真正掌握其中的奥妙,我们一开始不会也不用难过,多看看资料很快就能掌握的。直到被骂好几次后我们回去找相关资料,为什么设计PCB电容要就近摆放呢,等看了资料后就能了解一些,可是网上的资料很杂散,很少能找到一个很全方面讲解的。下面这些内容是我转载的一篇关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。老师问: 为什么去耦电容就近摆放呢?学生答: 因为它有有效半径哦,放的远了失效的。电容去耦的一个重要问题是电容的去耦半径。大多数资料中都会提到电容摆放要尽量靠近芯片,多数资料都是从减小回路电感的角度来谈这个摆放距离问题。确实,减小电感是一个重要原因,但是还有一个重要的原因大多数资料都没有提及,那就是电容去耦半径问题。如果电容摆放离芯片过远,超出了它的去耦半径,电容将失去它的去耦的作用。理解去耦半径最好的办法就是考察噪声源和电容补偿电流之间的相位关系。当芯片对电流的需求发生变化时,会在电源平面的一个很小的局部区域内产生电压扰动,电容要补偿这一电流(或电压),就必须先感知到这个电压扰动。信号在介质中传播需要一定的时间,因此从发生局部电压扰动到电容感知到这一扰动之间有一个时间延迟。同样,电容的补偿电流到达扰动区也需要一个延迟。因此必然造成噪声源和电容补偿电流之间的相位上的不一致。

在高速设计中,可控阻抗板和线路的特性阻抗问题困扰着许多中国工程师。本文通过简单而且直观的方法介绍了特性阻抗的基本性质、计算和测量方法。在高速设计中,可控阻抗板和线路的特性阻抗是最重要和最普遍的问题之一。首先了解一下传输线的定义:传输线由两个具有一定长度的导体组成,一个导体用来发送信号,另一个用来接收信号(切记“回路”取代“地”的概念)。在一个多层板中,每一条线路都是传输线的组成部分,邻近的参考平面可作为第二条线路或回路。一条线路成为“性能良好”传输线的关键是使它的特性阻抗在整个线路中保持恒定。线路板成为“可控阻抗板”的关键是使所有线路的特性阻抗满足一个规定值,通常在25欧姆和70欧姆之间。在多层线路板中,传输线性能良好的关键是使它的特性阻抗在整条线路中保持恒定。但是,究竟什么是特性阻抗?理解特性阻抗最简单的方法是看信号在传输中碰到了什么。当沿着一条具有同样横截面传输线移动时,这类似图1所示的微波传输。假定把1伏特的电压阶梯波加到这条传输线中,如把1伏特的电池连接到传输线的前端(它位于发送线路和回路之间),一旦连接,这个电压波信号沿着该线以光速传播,它的速度通常约为6英寸/纳秒。当然,这个信号确实是发送线路和回路之间的电压差,它可以从发送线路的任何一点和回路的相临点来衡量。图2是该电压信号的传输示意图。Zen的方法是先“产生信号”,然后沿着这条传输线以6英寸/纳秒的速度传播。第Y个0.01纳秒前进了0.06英寸,这时发送线路有多余的正电荷,而回路有多余的负电荷,正是这两种电荷差维持着这两个导体之间的1伏电压差,而这两个导体又组成了一个电容器。在下一个0.01纳秒中,又要将一段0.06英寸传输线的电压从0调整到1伏特,这必须加一些正电荷到发送线路,而加一些负电荷到接收线路。每移动0.06英寸,必须把更多的正电荷加到发送线路,而把更多的负电荷加到回路。每隔0.01纳秒,必须对传输线路的另外一段进行充电,然后信号开始沿着这一段传播。电荷来自传输线前端的电池,当沿着这条线移动时,就给传输线的连续部分充电,因而在发送线路和回路之间形成了1伏特的电压差。每前进0.01纳秒,就从电池中获得一些电荷(±Q),恒定的时间间隔(±t)内从电池中流出的恒定电量(±Q)就是一种恒定电流。流入回路的负电流实际上与流出的正电流相等,而且正好在信号波的前端,交流电流通过上、下线路组成的电容,结束整个循环过程。

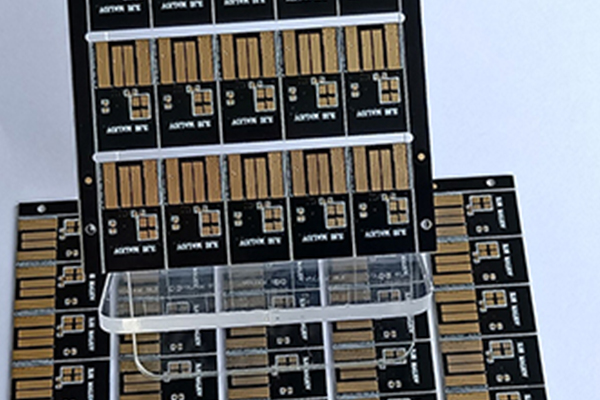

Via hole导通孔起线路互相连结导通的作用,电子行业的发展,同时也促进PCB的发展,也对印制板制作工艺和表面贴装技术提出更高要求。Via hole塞孔工艺应运而生,同时应满足下列要求:(一)导通孔内有铜即可,阻焊可塞可不塞;(二)导通孔内必须有锡铅,有一定的厚度要求(4微米),不得有阻焊油墨入孔,造成孔内藏锡珠;(三)导通孔必须有阻焊油墨塞孔,不透光,不得有锡圈,锡珠以及平整等要求。随着电子产品向“轻、薄、短、小”方向发展,PCB也向高密度、高难度发展,因此出现大量SMT、BGA的PCB,而客户在贴装元器件时要求塞孔,主要有五个作用:(一)防止PCB过波峰焊时锡从导通孔贯穿元件面造成短路;特别是我们把过孔放在BGA焊盘上时,就必须先做塞孔,再镀金处理,便于BGA的焊接。(二)避免助焊剂残留在导通孔内;(三)电子厂表面贴装以及元件装配完成后PCB在测试机上要吸真空形成负压才完成:(四)防止表面锡膏流入孔内造成虚焊,影响贴装;

pcn设计问题集第Y部分从pcb如何选材到运用等一系列问题进行总结。1、如何选择PCB板材?选择PCB板材必须在满足设计需求和可量产性及成本中间取得平衡点。设计需求包含电气和机构这两部分。通常在设计非常高速的PCB板子(大于GHz的频率)时这材质问题会比较重要。例如,现在常用的FR-4材质,在几个GHz的频率时的介质损耗(dielectric loss)会对信号衰减有很大的影响,可能就不合用。就电气而言,要注意介电常数(dielectric constant)和介质损在所设计的频率是否合用。2、如何避免高频干扰?避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces在模拟信号旁边。还要注意数字地对模拟地的噪声干扰。3、在高速设计中,如何解决信号的完整性问题?信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

安徽开发SMT贴片一、快速确定PCB外形设计PCB先要确定电路板的外形,通常就是在禁止布线层画出电气的布线范围开发SMT贴片。除非有特殊要求,一般电路板的形状都为矩形,长宽比一般为3:2或者4:3较为理想。在画之前可以任意画出两条横线和两条竖线,然后利用“放置工具条”里的“设置原点”工具将某一条线段的端点设为原点即坐标为(0,0),之后双击每一条线段,对其起点和终点的坐标值进行相应的更改,使4条线段首尾相接,形成一个封闭的矩形框,电路板的外型确定也就完成了。如果在画图的过程中需要调整电路板的大小,只要修改每条线段的相应坐标值即可。从成本、敷铜线长度、抗噪声能力考虑,电路板尺寸越小越好,但是板尺寸太小,则散热不良,且相邻的导线容易引起干扰。不过,当电路板的尺寸大于200mm×150mm时,应该考虑电路板的机械强度,适当加装固定孔,以便起到支撑的作用。二、元件布局开始布局之前首先要通过网络表载入元器件,这个过程中经常会遇到网络表无法完全载入的错误,主要可归为两类:一类是找不到元件,解决方法是确认原理图中已定义元件的封装形式,并确认已添加相应的PCB元件库,若仍找不到元件就要自己造一个元件封装了;另一类是丢失引脚,最常见的就是二极管、三极管的引脚丢失,这是由于原理图中的引脚一般是字母A、K、E、B、C,而PCB元件的引脚则是数字1、2、3,解决方法就是更改原理图的定义,或者更改PCB元件的定义使其一致即可。有经验的设计者一般都会根据实际元件的封装外形建立一个自己的PCB元件库,使用方便而且不易出错。进行布局时,必须要遵循一些基本规则:(1)特殊元件特殊考虑高频元件之间要尽量靠近,连线越短越好;具有高电位差的元件之间距离尽量加大;重量大的元器件应该有支架固定;发热的元件应远离热敏元件并加装相应的散热片或置于板外;电位器、可调电感线圈、可变电容、微动开关等可调元件的布局应该考虑整机的结构要求,以方便调节为准。总之,一些特殊的元器件在布局时要从元件本身的特性、机箱的结构、维修调试的方便性等多方面综合考虑,以保证做出一块稳定、好用的PCB板。