1)专门用于探测的测试焊盘的直径应该不小于0.9mm 。2) 测试焊盘周围的空间应大于0.6mm 而小于5mm 。如果元器件的高度大于6. 7mm,那么测试焊盘应置于该元器件5mm 以外。3) 在距离印制电路板边缘3mm 以内不要放置任何元器件或测试焊盘。4) 测试焊盘应放在一个网格中2.5mm孔的中心。如果有可能,允许使用标准探针和一个更可靠的固定装置。5) 不要依靠连接器指针的边缘来进行焊盘测试。测试探针很容易损坏镀金指针。6) 避免镀通孔-印制电路板两边的探查。把测试顶端通过孔放到印制电路板的非元器件/焊接面上。

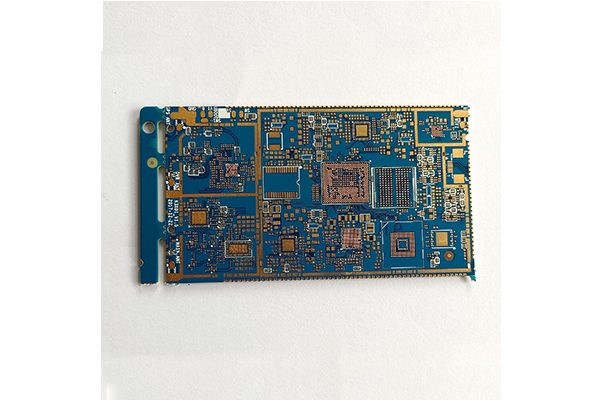

【第Y招】多层板布线高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 【第二招】高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 【第三招】高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 【第四招】高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。

在高速设计中,可控阻抗板和线路的特性阻抗问题困扰着许多中国工程师。本文通过简单而且直观的方法介绍了特性阻抗的基本性质、计算和测量方法。在高速设计中,可控阻抗板和线路的特性阻抗是最重要和最普遍的问题之一。首先了解一下传输线的定义:传输线由两个具有一定长度的导体组成,一个导体用来发送信号,另一个用来接收信号(切记“回路”取代“地”的概念)。在一个多层板中,每一条线路都是传输线的组成部分,邻近的参考平面可作为第二条线路或回路。一条线路成为“性能良好”传输线的关键是使它的特性阻抗在整个线路中保持恒定。线路板成为“可控阻抗板”的关键是使所有线路的特性阻抗满足一个规定值,通常在25欧姆和70欧姆之间。在多层线路板中,传输线性能良好的关键是使它的特性阻抗在整条线路中保持恒定。但是,究竟什么是特性阻抗?理解特性阻抗最简单的方法是看信号在传输中碰到了什么。当沿着一条具有同样横截面传输线移动时,这类似图1所示的微波传输。假定把1伏特的电压阶梯波加到这条传输线中,如把1伏特的电池连接到传输线的前端(它位于发送线路和回路之间),一旦连接,这个电压波信号沿着该线以光速传播,它的速度通常约为6英寸/纳秒。当然,这个信号确实是发送线路和回路之间的电压差,它可以从发送线路的任何一点和回路的相临点来衡量。图2是该电压信号的传输示意图。Zen的方法是先“产生信号”,然后沿着这条传输线以6英寸/纳秒的速度传播。第Y个0.01纳秒前进了0.06英寸,这时发送线路有多余的正电荷,而回路有多余的负电荷,正是这两种电荷差维持着这两个导体之间的1伏电压差,而这两个导体又组成了一个电容器。在下一个0.01纳秒中,又要将一段0.06英寸传输线的电压从0调整到1伏特,这必须加一些正电荷到发送线路,而加一些负电荷到接收线路。每移动0.06英寸,必须把更多的正电荷加到发送线路,而把更多的负电荷加到回路。每隔0.01纳秒,必须对传输线路的另外一段进行充电,然后信号开始沿着这一段传播。电荷来自传输线前端的电池,当沿着这条线移动时,就给传输线的连续部分充电,因而在发送线路和回路之间形成了1伏特的电压差。每前进0.01纳秒,就从电池中获得一些电荷(±Q),恒定的时间间隔(±t)内从电池中流出的恒定电量(±Q)就是一种恒定电流。流入回路的负电流实际上与流出的正电流相等,而且正好在信号波的前端,交流电流通过上、下线路组成的电容,结束整个循环过程。

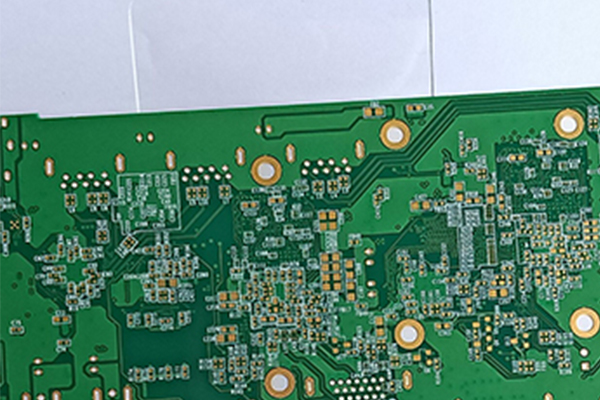

辽宁PCB电路板一个高明的CAD工程师需要做的是:如何综合考虑各方意见,达到最佳结合点。以下为EDADOC专家根据个人在通讯产品PCB设计的多年经验,开发PCB电路板所总结出来的层叠设计参考,与大家共享。 PCB层叠设计基本原则 CAD工程师在完成布局(或预布局)后,重点对本板的布线瓶径处进行分析,再结合EDA软件关于布线密度(PIN/RAT)的报告参数、综合本板诸如差分线、敏感信号线、特殊拓扑结构等有特殊布线要求的信号数量、种类确定布线层数;再根据单板的电源、地的种类、分布、有特殊布线需求的信号层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。单板层的排布一般原则:A)与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层布线提供回流平面;B)所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻);C)主电源尽可能与其对应地相邻;D)尽量避免两信号层直接相邻;

在PCB(印制电路板)中,印制导线用来实现电路元件和器件之间电气连接,是PCB中的重要组件,PCB导线多为铜线,铜自身的物理特性也导致其在导电过程中必然存在一定的阻抗,导线中的电感成分会影响电压信号的传输,而电阻成分则会影响电流信号的传输,在高频线路中电感的影响尤为严重,因此,在PCB设计中必须注意和消除印制导线阻抗所带来的影响。1印制导线产生干扰的原因PCB上的印制导线通电后在直流或交流状态下分别对电流呈现电阻或感抗,而平行导线之间存在电感效应,电阻效应,电导效应,互感效应;一根导线上的变化电流必然影响另一根导线,从而产生干扰;PCB板外连接导线甚至元器件引线都可能成为发射或接收干扰信号的天线。印制导线的直流电阻和交流阻抗可以通过公式和公式来计算,R=PL/S和XL=2πfL式中L为印制导线长度(m),s为导线截面积(mm2),ρ为铜的电阻率,TT为常数,f为交流频率。正是由于这些阻抗的存在,从而产生一定的电位差,这些电位差的存在,必然会带来干扰,从而影响电路的正常工作。2 PCB电流与导线宽度的关系PCB导线宽度与电路电流承载值有关,一般导线越宽,承载电流的能力越强。在实际的PCB制作过程中,导线宽度应以能满足电气性能要求而又便于生产为宜,它的最小值以承受的电流大小而定,导线宽度和间距可取0.3mm(12mil)。导线的宽度在大电流的情况下还要考虑其温升问题。PCB设计铜铂厚度、线宽