1、PTH造成的孔壁镀层空洞PTH造成的孔壁镀层空洞主要是点状的或环状的空洞,具体产生的原因如下:(1)沉铜缸铜含量、氢氧化钠与甲醛的浓度铜缸的溶液浓度是首先要考虑的。一般来说,铜含量、氢氧化钠与甲醛的浓度是成比例的,当其中的任何一种含量低于标准数值的10%时都会破坏化学反应的平衡,造成化学铜沉积不良,出现点状的空洞。所以优先考虑调整铜缸的各药水参数。(2)槽液的温度槽液的温度对溶液的活性也存在着重要的影响。在各溶液中一般都会有温度的要求,其中有些是要严格控制的。所以对槽液的温度也要随时关注。(3)活化液的控制二价锡离子偏低会造成胶体钯的分解,影响钯的吸附,但只要对活化液定时的进行添加补充,不会造成大的问题。活化液控制的重点是不能用空气搅拌,空气中的氧会氧化二价锡离子,同时也不能有水进入,会造成SnCl2的水解。(4)清洗的温度清洗的温度常常被人忽视,清洗的最佳温度是在20℃以上,若低于15℃就会影响清洗的效果。在冬季的时候,水温会变的很低,尤其是在北方。由于水洗的温度低,板子在清洗后的温度也会变的很低,在进入铜缸后板子的温度不能立刻升上来,会因为错过了铜沉积的黄金时间而影响沉积的效果。所以在环境温度较低的地方,也要注意清洗水的温度。(5)整孔剂的使用温度、浓度与时间药液的温度有着较严格的要求,过高的温度会造成整孔剂的分解,使整孔剂的浓度变低,影响整孔的效果,其明显的特征是在孔内的玻璃纤维布处出现点状空洞。只有药液的温度、浓度与时间妥善的配合,才能得到良好的整孔效果,同时又能节约成本。药液中不断累积的铜离子浓度,也必须严格控制。(6)还原剂的使用温度、浓度与时间还原的作用是去除去钻污后残留的锰酸钾和高锰酸钾,药液相关参数的失控都会影响其作用,其明显的特征是在孔内的树脂处出现点状空洞。(7)震荡器和摇摆

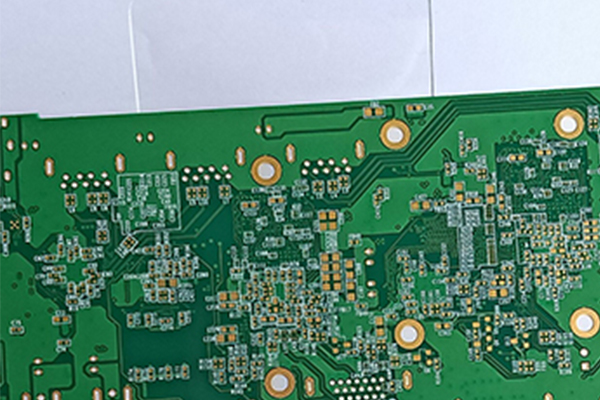

一个高明的CAD工程师需要做的是:如何综合考虑各方意见,达到最佳结合点。以下为EDADOC专家根据个人在通讯产品PCB设计的多年经验,所总结出来的层叠设计参考,与大家共享。 PCB层叠设计基本原则 CAD工程师在完成布局(或预布局)后,重点对本板的布线瓶径处进行分析,再结合EDA软件关于布线密度(PIN/RAT)的报告参数、综合本板诸如差分线、敏感信号线、特殊拓扑结构等有特殊布线要求的信号数量、种类确定布线层数;再根据单板的电源、地的种类、分布、有特殊布线需求的信号层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。单板层的排布一般原则:A)与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层布线提供回流平面;B)所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻);C)主电源尽可能与其对应地相邻;D)尽量避免两信号层直接相邻;

通讯与计算机技术的高速发展使得高速PCB设计进入了千兆位领域,新的高速器件应用使得如此高的速率在背板和单板上的长距离传输成为可能,但与此同时,PCB设计中的信号完整性问题(SI)、电源完整性以及电磁兼容方面的问题也更加突出。信号完整性是指信号在信号线上传输的质量,主要问题包括反射、振荡、时序、地弹和串扰等。信号完整性差不是由某个单一因素导致,而是板级设计中多种因素共同引起。在千兆位设备的PCB板设计中,一个好的信号完整性设计要求工程师全面考虑器件、传输线互联方案、电源分配以及EMC方面的问题。高速PCB设计EDA工具已经从单纯的仿真验证发展到设计和验证相结合,帮助设计者在设计早期设定规则以避免错误而不是在设计后期发现问题。随着数据速率越来越高设计越来越复杂,高速PCB系统分析工具变得更加必要,这些工具包括时序分析、信号完整性分析、设计空间参数扫描分析、EMC设计、电源系统稳定性分析等。这里我们将着重讨论在千兆位设备PCB设计中信号完整性分析应考虑的一些问题。高速器件与器件模型尽管千兆位发送与接收元器件供应商会提供有关芯片的设计资料,但是器件供应商对于新器件信号完整性的了解也存在一个过程,这样器件供应商给出的设计指南可能并不成熟,还有就是器件供应商给出的设计约束条件通常都是非常苛刻的,对设计工程师来说要满足所有的设计规则会非常困难。所以就需要信号完整性工程师运用仿真分析工具对供应商的约束规则和实际设计进行分析,考察和优化元器件选择、拓扑结构、匹配方案、匹配元器件的值,并最终开发出确保信号完整性的PCB布局布线规则。因此,千兆位信号的精确仿真分析变得十分重要,而器件模型在信号完整性分析工作中的作用也越来越得到重视。

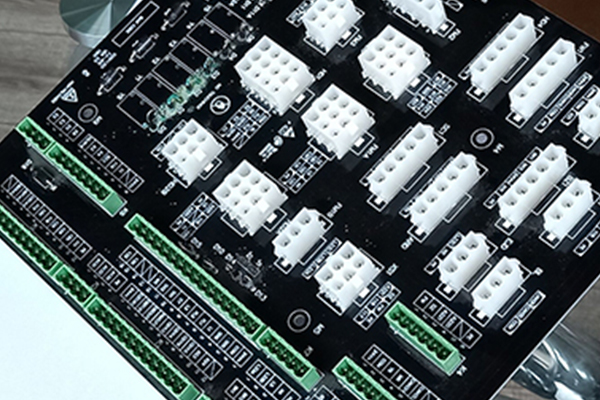

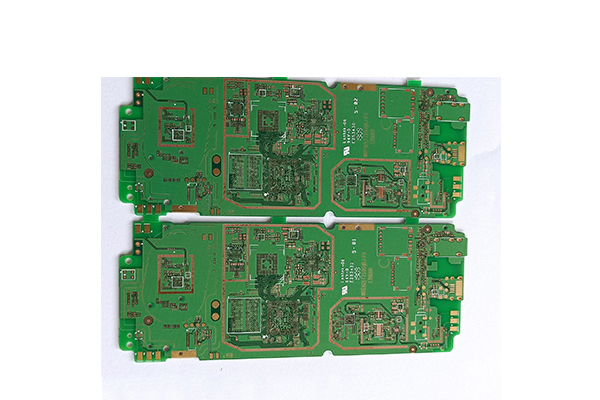

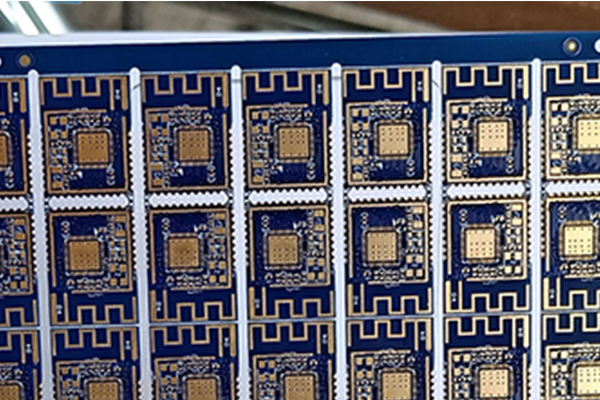

专业PCB电路板1.开料目的:根据工程资料MI的要求,在符合要求的大张板材上,PCB电路板生产商裁切成小块生产板件.符合客户要求的小块板料.流程:大板料→按MI要求切板→锔板→啤圆角磨边→出板钻孔目的:根据工程资料,在所开符合要求尺寸的板料上,相应的位置钻出所求的孔径.流程:叠板销钉→上板→钻孔→下板→检查修理沉铜目的:沉铜是利用化学方法在绝缘孔壁上沉积上一层薄铜.流程:粗磨→挂板→沉铜自动线→下板→浸%稀H2SO4→加厚铜图形转移目的:图形转移是生产菲林上的图像转移到板上。流程:(蓝油流程):磨板→印第Y面→烘干→印第二面→烘干→爆光→冲影→检查;(干膜流程):麻板→压膜→静置→对位→曝光→静置→冲影→检查图形电镀目的:图形电镀是在线路图形裸露的铜皮上或孔壁上电镀一层达到要求厚度的铜层与要求厚度的金镍或锡层。流程:上板→除油→水洗二次→微蚀→水洗→酸洗→镀铜→水洗→浸酸→镀锡→水洗→下板退膜目的:用NaOH溶液退去抗电镀覆盖膜层使非线路铜层裸露出来。流程:水膜:插架→浸碱→冲洗→擦洗→过机;干膜:放板→过机蚀刻目的:蚀刻是利用化学反应法将非线路部位的铜层腐蚀去。绿油目的:绿油是将绿油菲林的图形转移到板上,起到保护线路和阻止焊接零件时线路上锡的作用。流程:磨板→印感光绿油→锔板→曝光→冲影;磨板→印第Y面→烘板→印第二面→烘板字符目的:字符是提供的一种便于辩认的标记。流程:绿油终锔后→冷却静置→调网→印字符→后锔镀金手指目的:在插头手指上镀上一层要求厚度的镍金层,使之更具有硬度的耐磨性。流程:上板→除油→水洗两次→微蚀→水洗两次→酸洗→镀铜→水洗→镀镍→水洗→镀金镀锡板 (并列的一种工艺)目的:喷锡是在未覆盖阻焊油的裸露铜面上喷上一层铅锡,以保护铜面不蚀氧化,以保证具有良好的焊接性能.流程:微蚀→风干→预热→松香涂覆→焊锡涂覆→热风平整→风冷→洗涤风干成型目的:通过模具冲压或数控锣机锣出客户所需要的形状成型的方法有机锣,啤板,手锣,手切说明:数据锣机板与啤板的精确度较高,手锣其次,手切板最低具只能做一些简单的外形.测试目的:通过电子00%测试,检测目视不易发现到的开路,短路等影响功能性之缺陷.流程:上模→放板→测试→合格→FQC目检→不合格→修理→返测试→OK→REJ→报废终检目的:通过00%目检板件外观缺陷,并对轻微缺陷进行修理,避免有问题及缺陷板件流出.具体工作流程:来料→查看资料→目检→合格→FQA抽查→合格→包装→不合格→处理→检查OKa

【第Y招】多层板布线高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 【第二招】高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 【第三招】高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 【第四招】高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。

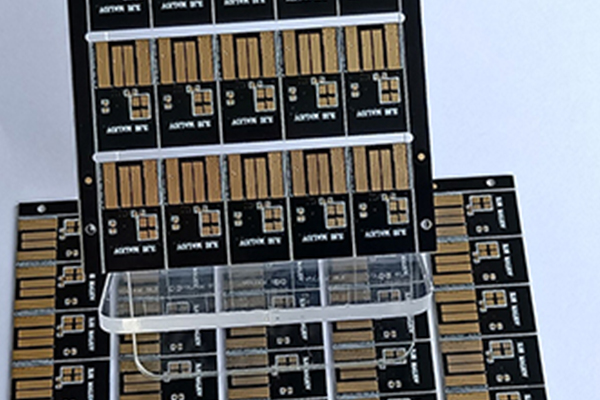

Via hole导通孔起线路互相连结导通的作用,电子行业的发展,同时也促进PCB的发展,也对印制板制作工艺和表面贴装技术提出更高要求。Via hole塞孔工艺应运而生,同时应满足下列要求:(一)导通孔内有铜即可,阻焊可塞可不塞;(二)导通孔内必须有锡铅,有一定的厚度要求(4微米),不得有阻焊油墨入孔,造成孔内藏锡珠;(三)导通孔必须有阻焊油墨塞孔,不透光,不得有锡圈,锡珠以及平整等要求。随着电子产品向“轻、薄、短、小”方向发展,PCB也向高密度、高难度发展,因此出现大量SMT、BGA的PCB,而客户在贴装元器件时要求塞孔,主要有五个作用:(一)防止PCB过波峰焊时锡从导通孔贯穿元件面造成短路;特别是我们把过孔放在BGA焊盘上时,就必须先做塞孔,再镀金处理,便于BGA的焊接。(二)避免助焊剂残留在导通孔内;(三)电子厂表面贴装以及元件装配完成后PCB在测试机上要吸真空形成负压才完成:(四)防止表面锡膏流入孔内造成虚焊,影响贴装;