(一) 画好原理图很多工程师都觉得layout工作更重要一些,原理图就是为了生成网表方便PCB做检查用的。其实,在后续电路调试过程中原理图的作用会更大一些。无论是查找问题还是和同事交流,还是原理图更直观更方便。另外养成在原理图中做标注的习惯,把各部分电路在layout的时候要注意到的问题标注在原理图上,对自己或者对别人都是一个很好的提醒。层次化原理图,把不同功能不同模块的电路分成不同的页,这样无论是读图还是以后重复使用都能明显的减少工作量。使用成熟的设计总是要比设计新电路的风险小。每次看到把所有电路都放在一张图纸上,一片密密麻麻的器件,脑袋就能大一圈。(二) 好好进行电路布局心急的工程师画完原理图,把网表导入PCB后就迫不及待的把器件放好,开始拉线。其实一个好的PCB布局能让你后面的拉线工作变得简单,让你的PCB工作的更好。每一块板子都会有一个信号路径,PCB布局也应该尽量遵循这个信号路径,让信号在板子上可以顺畅的传输,人们都不喜欢走迷宫,信号也一样。如果原理图是按照模块设计的,PCB也一样可以。按照不同的功能模块可以把板子划分为若干区域。模拟数字分开,电源信号分开,发热器件和易感器件分开,体积较大的器件不要太靠近板边,注意射频信号的屏蔽等等……多花一分的时间去优化PCB的布局,就能在拉线的时候节省更多的时间。

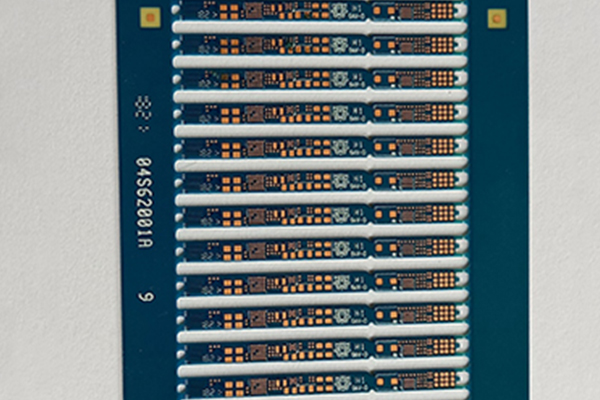

一、拿一块PCB板,首先需要在纸上记录好所有元气件的型号,参数以及位置,尤其是二极管、三级管的方向,IC缺口的方向。最好用数码相机拍两张元器件位置的照片。二、拆掉所有元件,要将PAD孔里的锡去掉。用酒精将板子擦洗干净,然后放入扫描仪,在扫描仪扫描的时候要稍调高一下扫描的像素,得到较清晰的板子图像。再用水纱纸将顶层和底层轻微打磨,打磨到铜膜发亮,放入扫描仪,启动PHOTOSHOP,用彩色方式将两层分别扫入。注意,PCB在扫描仪内摆放一定要横平竖直,否则扫描的图象就无法使用。三、调整画布的对比度,明暗度,使有铜膜的部分和没有铜膜的部分形成强烈对比,然后将图转为黑白,检查线条是否清晰,如果不清晰,就要继续调节。如果清晰,将图存为黑白BMP格式两个文件,如果发现图形有问题,还需用PHOTOSHOP进行修正。四、将两个BMP格式的文件分别转为PROTEL格式文件,在PROTEL中调入两层,如果两层的PAD和VIA的位置基本重合,表明前几个步骤做的很好,如果有偏差,则重复第三步,直到吻合为止,将TOP层的BMP转化为TOP.PCB,注意要转化到SILK层,就是黄色的那层,然后你在TOP层描线就是了,并且根据第二步的图纸放置器件。画完后将SILK层删掉,不断重复知道绘制好所有的层。五、在PROTEL中将TOP.PCB和BOT.PCB调入,合为一个图就OK了。用激光打印机将TOP LAYER,BOTTOM LAYER分别打印到透明胶片上(1:1的比例),把胶片放到那块PCB上,比较一下是否有误,如果没错,就算成功。

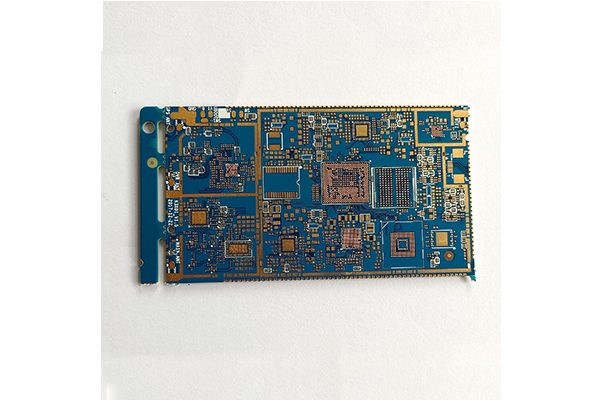

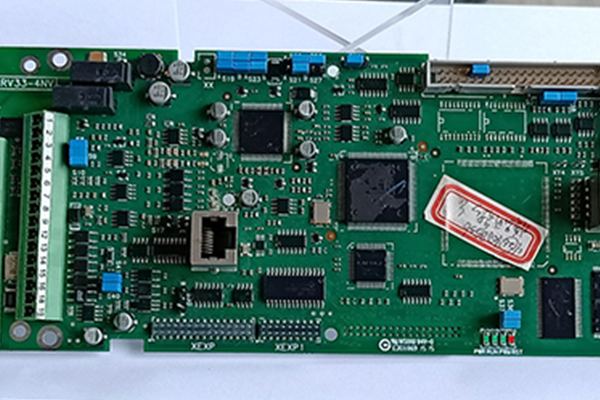

重庆开发电路板组装测试从IC芯片的发展及封装形式来看,芯片体积越来越小、引脚数越来越多;同时,由于近年来IC工艺的发展,使得其速度也越来越高。电路板组装测试生产商这就带来了一个问题,即电子设计的体积减小导致电路的布局布线密度变大,而同时信号的频率还在提高,从而使得如何处理高速信号问题成为一个设计能否成功的关键因素。随着电子系统中逻辑复杂度和时钟频率的迅速提高,信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要。对于低频设计,线迹互连和板层的影响可以不考虑,但当频率超过50 MHz时,互连关系必须考虑,而在*定系统性能时还必须考虑印刷电路板板材的电参数。因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性(Signal Integrity,SI)问题。当硬件工作频率增高后,每一根布线网络上的传输线都可能成为发射天线,对其他电子设备产生电磁辐射或与其他设备相互干扰,从而使硬件时序逻辑产生混乱。电磁兼容性(Electromagnetic Compatibility,EMC)的标准提出了解决硬件实际布线网络可能产生的电磁辐射干扰以及本身抵抗外部电磁干扰的基本要求。1 高速数字电路设计的几个基本概念在高速数字电路中,由于串扰、反射、过冲、振荡、地弹、偏移等信号完整性问题,本来在低速电路中无需考虑的因素在这里就显得格外重要;另外,随着现有电气系统耦合结构越来越复杂,电磁兼容性也变成了一个不能不考虑的问题。要解决高速电路设计的问题,首先需要真正明白高速信号的概念。高速不是就频率的高低来说的,而是由信号的边沿速度决定的,一般认为上升时间小于4倍信号传输延迟时可视为高速信号。即使在工作频率不高的系统中,也会出现信号完整性的问题。这是由于随着集成电路工艺的提高,所用器件I/O端口的信号边沿比以前更陡更快,因此在工作时钟不高的情况下也属于高速器件,随之带来了信号完整性的种种问题。

在基于信号完整性计算机分析的PCB设计方法中,最为核心的部分就是PCB板级信号完整性模型的建立,这是与传统的设计方法的区别之处。SI模型的正确性将决定设计的正确性,而SI模型的可建立性则决定了这种设计方法的可行性。目前构成器件模型的方法有两种:一种是从元器件的电学工作特性出发,把元器件看成‘黑盒子’,测量其端口的电气特性,提取器件模型,而不涉及器件的工作原理,称为行为级模型。这种模型的代表是IBIS模型和S参数。其优点是建模和使用简单方便,节约资源,适用范围广泛,特别是在高频、非线性、大功率的情况下行为级模型是一个选择。缺点是精度较差,一致性不能保证,受测试技术和精度的影响。另一种是以元器件的工作原理为基础,从元器件的数学方程式出发,得到的器件模型及模型参数与器件的物理工作原理有密切的关系。SPICE 模型是这种模型中应用最广泛的一种。其优点是精度较高,特别是随着建模手段的发展和半导体工艺的进步和规范,人们已可以在多种级别上提供这种模型,满足不同的精度需要。缺点是模型复杂,计算时间长。一般驱动器和接收器的模型由器件厂商提供,传输线的模型通常从场分析器中提取,封装和连接器的模型即可以由场分析器提取,又可以由制造厂商提供。在电子设计中已经有多种可以用于PCB板级信号完整性分析的模型,其中最为常用的有三种,分别是SPICE、IBIS和Verilog-AMS、VHDL-AMS。