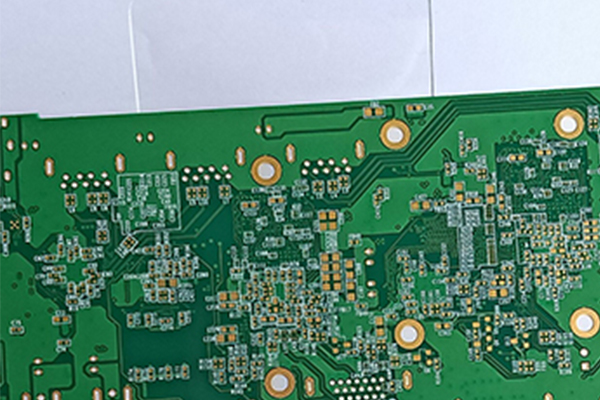

【第Y招】多层板布线高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须,也是降低干扰的有效手段。在PCB Layout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。有资料显示,同种材料时,四层板要比双面板的噪声低20dB。但是,同时也存在一个问题,PCB半层数越高,制造工艺越复杂,单位成本也就越高,这就要求我们在进行PCB Layout时,除了选择合适的层数的PCB板,还需要进行合理的元器件布局规划,并采用正确的布线规则来完成设计。 【第二招】高速电子器件管脚间的引线弯折越少越好 高频电路布线的引线最好采用全直线,需要转折,可用45度折线或者圆弧转折,这种要求在低频电路中仅仅用于提高铜箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。 【第三招】高频电路器件管脚间的引线越短越好 信号的辐射强度是和信号线的走线长度成正比的,高频的信号引线越长,它就越容易耦合到靠近它的元器件上去,所以对于诸如信号的时钟、晶振、DDR的数据、LVDS线、USB线、HDMI线等高频信号线都是要求尽可能的走线越短越好。 【第四招】高频电路器件管脚间的引线层间交替越少越好 所谓“引线的层间交替越少越好”是指元件连接过程中所用的过孔(Via)越少越好。据侧,一个过孔可带来约0.5pF的分布电容,减少过孔数能显著提高速度和减少数据出错的可能性。

这里主要是说了从PCB设计封装来解析选择元件的技巧。元件的封装包含很多信息,包含元件的尺寸,特别是引脚的相对位置关系,还有元件的焊盘类型。当然我们根据元件封装选择元件时还有一个要注意的地方是要考虑元件的外形尺寸。引脚位置关系:主要是指我们需要将实际的元件的引脚和PCB元件的封装的尺寸对应起来。我们选择不同的元件,虽然功能相同,但是元件的封装很可能不一样。我们需要保证PCB焊盘尺寸位置正确才能保证元件能正确焊接。焊盘的选择:这个是我们需要考虑的比较多的地方。首先包括焊盘的类型。其类型包括两种,一是电镀通孔,一种是表贴类型。我们需要考虑的因素有器件成本、可用性、器件面积密度和功耗等因数。从制造角度看,表贴器件通常要比通孔器件便宜,而且一般可用性较高。对于我们一般设计来说,我们选择表贴元件,不仅方便手工焊接,而且有利于查错和调试过程中更好的连接焊盘和信号。其次我们还应该注意焊盘的位置。因为不同的位置,就代表元件实际当中不同的位置。我们如果不合理安排焊盘的位置,很有可能就会出现一个区域元件过密,而另外一个区域元件很稀疏的情况,当然情况更糟糕的是由于焊盘位置过近,导致元件之间空隙过小而无法焊接,下面就是我失败的一个例子,我在一个光耦开关旁边开了通孔,但是由于它们的位置过近,导致光耦开关焊接上去以后,通孔无法再放置螺丝了。

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。1、尽可能使用多层PCB相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100。尽量地将每一个信号层都紧靠一个电源层或地线层。对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。2、对于双面PCB来说,要采用紧密交织的电源和地栅格。电源线紧靠地线,在垂直和水平线或填充区之间,要尽可能多地连接。一面的栅格尺寸小于等于60mm,如果可能,栅格尺寸应小于13mm。3、确保每一个电路尽可能紧凑。4、尽可能将所有连接器都放在一边。5、在每一层的机箱地和电路地之间,要设置相同的“隔离区”;如果可能,保持间隔距离为0.64mm。6、PCB装配时,不要在顶层或者底层的焊盘上涂覆任何焊料。使用具有内嵌垫圈的螺钉来实现PCB与金属机箱/屏蔽层或接地面上支架的紧密接触。

台湾专业PCB铝基板解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。PCB铝基板生产商本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧。电源汇流排在IC的电源引脚附近合理地安置适当容量的电容,可使IC输出电压的跳变来得更快。然而,问题并非到此为止。由于电容呈有限频率响应的特性,这使得电容无法在全频带上生成干净地驱动IC输出所需要的谐波功率。除此之外,电源汇流排上形成的瞬态电压在去耦路径的电感两端会形成电压降,这些瞬态电压就是主要的共模EMI干扰源。我们应该怎么解决这些问题?就我们电路板上的IC而言,IC周围的电源层可以看成是优良的高频电容器,它可以收集为干净输出提供高频能量的分立电容器所泄漏的那部份能量。此外,优良的电源层的电感要小,从而电感所合成的瞬态信号也小,进而降低共模EMI。当然,电源层到IC电源引脚的连线必须尽可能短,因为数位信号的上升沿越来越快,最好是直接连到IC电源引脚所在的焊盘上,这要另外讨论。为了控制共模EMI,电源层要有助于去耦和具有足够低的电感,这个电源层必须是一个设计相当好的电源层的配对。有人可能会问,好到什么程度才算好?问题的答案取决于电源的分层、层间的材料以及工作频率(即IC上升时间的函数)。通常,电源分层的间距是6mil,夹层是FR4材料,则每平方英寸电源层的等效电容约为75pF。显然,层间距越小电容越大。

一个高明的CAD工程师需要做的是:如何综合考虑各方意见,达到最佳结合点。以下为EDADOC专家根据个人在通讯产品PCB设计的多年经验,所总结出来的层叠设计参考,与大家共享。 PCB层叠设计基本原则 CAD工程师在完成布局(或预布局)后,重点对本板的布线瓶径处进行分析,再结合EDA软件关于布线密度(PIN/RAT)的报告参数、综合本板诸如差分线、敏感信号线、特殊拓扑结构等有特殊布线要求的信号数量、种类确定布线层数;再根据单板的电源、地的种类、分布、有特殊布线需求的信号层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。单板层的排布一般原则:A)与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层布线提供回流平面;B)所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻);C)主电源尽可能与其对应地相邻;D)尽量避免两信号层直接相邻;