一个布局是否合理没有判断标准,可以采用一些相对简单的标准来判断布局的优劣。最常用的标准就是使飞线总长度尽可能短。一般来说,飞线总长度越短,意味着布线总长度也是越短(注意:这只是相对于大多数情况是正确的,并不是完全正确);走线越短,走线所占据的印制板面积也就越小,布通率越高。在走线尽可能短的同时,还必须考虑布线密度的问题。如何布局才能使飞线总长度最短并且保证布局密度不至于过高而不能实现是个很复杂的问题。因为,调整布局就是调整封装的放置位置,一个封装的焊盘往往和几个甚至几十个网络同时相关联,减小一个网络飞线长度可能会增长另一个网络的飞线长度。如何能够调整封装的位置到最佳点实在给不出太实用的标准,实际操作时,主要依靠设计者的经验观查屏幕显示的飞线是否简捷、有序和计算出的总长度是否最短。飞线是手工布局和布线的主要参考标准,手工调整布局时尽量使飞线走最短路径,手工布线时常常按照飞线指示的路径连接各个焊盘。Protel的飞线优化算法可以有效地解决飞线连接的最短路径问题。飞线的连接策略Protel提供了两种飞线连接方式供使用者选择:顺序飞线和最短树飞线。在布线参数设置中的飞线模式页可以设置飞线连接策略,应该选择最短树策略。动态飞线在有关飞线显示和控制一节中已经讲到: 执行显示网络飞线、显示封装飞线和显示全部飞线命令之一后飞线显示开关打开,执行隐含全部飞线命令后飞线显示开关关闭。

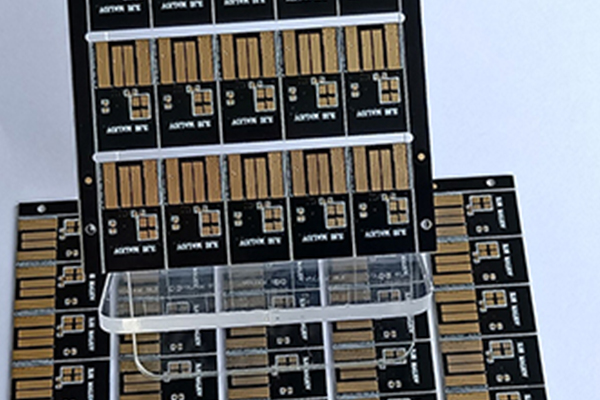

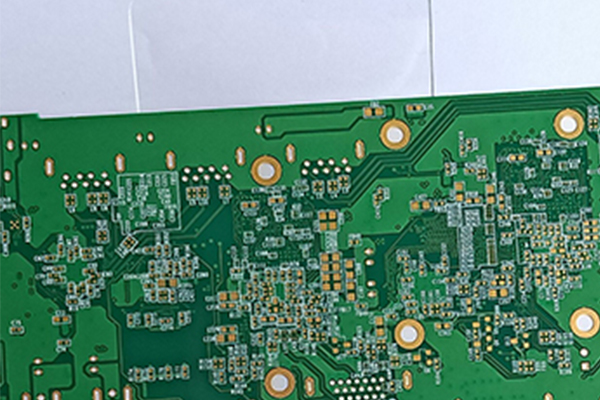

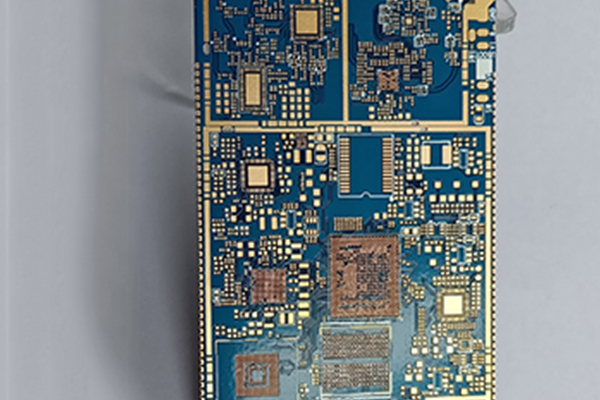

重庆厂家SMT贴片一、PCB沉金采用的是化学沉积的方法,通过化学氧化还原反应的方法生成一层镀层,一般厚度较厚,厂家SMT贴片是化学镍金金层沉积方法的一种,可以达到较厚的金层。二、PCB镀金采用的是电解的原理,也叫电镀方式。其他金属表面处理也多数采用的是电镀方式。在实际产品应用中,90%的金板是沉金板,因为镀金板焊接性差是他的致命缺点,也是导致很多公司放弃镀金工艺的直接原因!沉金工艺在印制线路表面上沉积颜色稳定,光亮度好,镀层平整,可焊性良好的镍金镀层。基本可分为四个阶段:前处理(除油,微蚀,活化、后浸),沉镍,沉金,后处理(废金水洗,DI水洗,烘干)。沉金厚度在0.025-0.1um间。金应用于电路板表面处理,因为金的导电性强,抗氧化性好,寿命长,而镀金板与沉金板最根本的区别在于,镀金是硬金(耐磨),沉金是软金(不耐磨)。1、沉金与镀金所形成的晶体结构不一样,沉金对于金的厚度比镀金要厚很多,沉金会呈金黄色,较镀金来说更黄(这是区分镀金和沉金的方法之一),镀金的会稍微发白(镍的颜色)。2、沉金与镀金所形成的晶体结构不一样,沉金相对镀金来说更容易焊接,不会造成焊接不良。沉金板的应力更易控制,对有邦定的产品而言,更有利于邦定的加工。同时也正因为沉金比镀金软,所以沉金板做金手指不耐磨(沉金板的缺点)。3、PCB沉金板只有焊盘上有镍金,趋肤效应中信号的传输是在铜层不会对信号有影响。4、沉金较镀金来说晶体结构更致密,不易产成氧化。5、随着电路板加工精度要求越来越高,线宽、间距已经到了0.1mm以下。镀金则容易产生金丝短路。沉金板只有焊盘上有镍金,所以不容易产成金丝短路。

1. 如果是人工焊接,要养成好的习惯,首先,焊接前要目视检查一遍PCB板,并用万用表检查关键电路(特别是电源与地)是否短路;其次,每次焊接完一个芯片就用万用表测一下电源和地是否短路;此外,焊接时不要乱甩烙铁,如果把焊锡甩到芯片的焊脚上(特别是表贴元件),就不容易查到。2. 在计算机上打开PCB图,点亮短路的网络,看什么地方离的最近,最容易被连到一块。特别要注意IC内部短路。3. 发现有短路现象。拿一块板来割线(特别适合单/双层板),割线后将每部分功能块分别通电,一部分一部分排除。4. 使用短路定位分析仪,如:新加坡PROTEQ CB2000短路追踪仪,香港灵智科技QT50短路追踪仪,英国POLAR ToneOhm950多层板路短路探测仪等等。5. 如果有BGA芯片,由于所有焊点被芯片覆盖看不见,而且又是多层板(4层以上),因此最好在设计时将每个芯片的电源分割开,用磁珠或0欧电阻连接,这样出现电源与地短路时,断开磁珠检测,很容易定位到某一芯片。由于BGA的焊接难度大,如果不是机器自动焊接,稍不注意就会把相邻的电源与地两个焊球短路。

覆铜,就是将PCB上闲置的空间作为基准面,然后用固体铜填充,这些铜区又称为灌铜。敷铜的意义在于,减小地线阻抗,提高抗干扰能力;降低压降,提高电源效率;还有,与地线相连,减小环路面积。如果PCB的地较多,有SGND、AGND、GND,等等,如何覆铜?我的做法是,根据PCB板面位置的不同,分别以最主要的“地”作为基准参考来独立覆铜,数字地和模拟地分开来敷铜自不多言。同时在覆铜之前,首先加粗相应的电源连线:V5.0V、V3.6V、V3.3V(SD卡供电),等等。这样一来,就形成了多个不同形状的多变形结构。覆铜需要处理好几个问题:一是不同地的单点连接,二是晶振附近的覆铜,电路中的晶振为一高频发射源,做法是在环绕晶振敷铜,然后将晶振的外壳另行接地。三是孤岛(死区)问题,如果觉得很大,那就定义个地过孔添加进去也费不了多大的事。另外,大面积覆铜好还是网格覆铜好,不好一概而论。为什么呢?大面积覆铜,如果过波峰焊时,板子就可能会翘起来,甚至会起泡。从这点来说,网格的散热性要好些。通常是高频电路对抗干扰要求高的多用网格,低频电路有大电流的电路等常用完整的铺铜。补充下:在数字电路中,特别是带MCU的电路中,兆级以上工作频率的电路,敷铜的作用就是为了降低整个地平面的阻抗。更具体的处理方法我一般是这样来操作的:各个核心模块(也都是数字电路)在允许的情况下也会分区敷铜,然后再用线把各个敷铜连接起来,这样做的目的也是为了减小各级电路之间的影响。对于数字电路模拟电路 混合的电路,地线的独立走线,以及到最后到电源滤波电容处的汇总就不多说了,大家都清楚。不过有一点:模拟电路里的地线分布,很多时候不能简单敷成一片铜皮就了事,因为模拟电路里很注重前后级的互相影响,而且模拟地也要求单点接地,所以能不能把模拟地敷成铜皮还得根据实际情况处理。(这就要求对所用到的模拟IC的一些特殊性能还是要了解的)

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响.因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:1、阻抗匹配2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇行线就是为了适应PCI33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

随着集成电路输出开关速度提高以及PCB板密度增加,信号完整性已经成为高速数字PCB设计必须关心的问题之一。元器件和PCB板的参数、元器件在PCB板上的布局、高速信号的布线等因素,都会引起信号完整性问题,导致系统工作不稳定,甚至完全不工作。如何在PCB板的设计过程中充分考虑到信号完整性的因素,并采取有效的控制措施,已经成为当今PCB设计业界中的一个热门课题。基于信号完整性计算机分析的高速数字PCB板设计方法能有效地实现PCB设计的信号完整性。1. 信号完整性问题概述信号完整性(SI)是指信号在电路中以正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题主要表现为5个方面:延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)。延迟是指信号在PCB板的导线上以有限的速度传输,信号从发送端发出到达接收端,其间存在一个传输延迟。信号的延迟会对系统的时序产生影响,在高速数字系统中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。另外,当PCB板上导线(高速数字系统中称为传输线)的特征阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使信号波形发生畸变,甚至出现信号的过冲和下冲。信号如果在传输线上来回反射,就会产生振铃和环绕振荡。