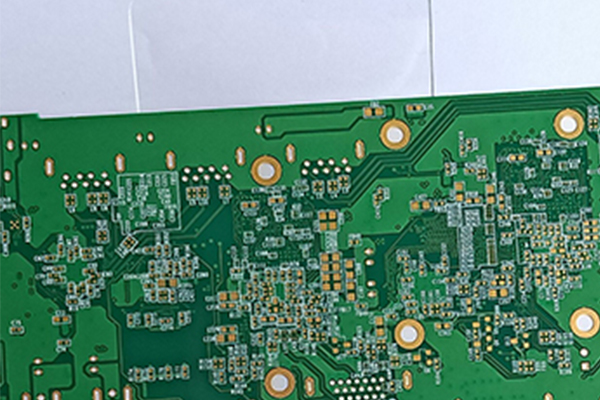

解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧。电源汇流排在IC的电源引脚附近合理地安置适当容量的电容,可使IC输出电压的跳变来得更快。然而,问题并非到此为止。由于电容呈有限频率响应的特性,这使得电容无法在全频带上生成干净地驱动IC输出所需要的谐波功率。除此之外,电源汇流排上形成的瞬态电压在去耦路径的电感两端会形成电压降,这些瞬态电压就是主要的共模EMI干扰源。我们应该怎么解决这些问题?就我们电路板上的IC而言,IC周围的电源层可以看成是优良的高频电容器,它可以收集为干净输出提供高频能量的分立电容器所泄漏的那部份能量。此外,优良的电源层的电感要小,从而电感所合成的瞬态信号也小,进而降低共模EMI。当然,电源层到IC电源引脚的连线必须尽可能短,因为数位信号的上升沿越来越快,最好是直接连到IC电源引脚所在的焊盘上,这要另外讨论。为了控制共模EMI,电源层要有助于去耦和具有足够低的电感,这个电源层必须是一个设计相当好的电源层的配对。有人可能会问,好到什么程度才算好?问题的答案取决于电源的分层、层间的材料以及工作频率(即IC上升时间的函数)。通常,电源分层的间距是6mil,夹层是FR4材料,则每平方英寸电源层的等效电容约为75pF。显然,层间距越小电容越大。

一个高明的CAD工程师需要做的是:如何综合考虑各方意见,达到最佳结合点。以下为EDADOC专家根据个人在通讯产品PCB设计的多年经验,所总结出来的层叠设计参考,与大家共享。 PCB层叠设计基本原则 CAD工程师在完成布局(或预布局)后,重点对本板的布线瓶径处进行分析,再结合EDA软件关于布线密度(PIN/RAT)的报告参数、综合本板诸如差分线、敏感信号线、特殊拓扑结构等有特殊布线要求的信号数量、种类确定布线层数;再根据单板的电源、地的种类、分布、有特殊布线需求的信号层数,综合单板的性能指标要求与成本承受能力,确定单板的电源、地的层数以及它们与信号层的相对排布位置。单板层的排布一般原则:A)与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层布线提供回流平面;B)所有信号层尽可能与地平面相邻(确保关键信号层与地平面相邻);C)主电源尽可能与其对应地相邻;D)尽量避免两信号层直接相邻;

一个布局是否合理没有判断标准,可以采用一些相对简单的标准来判断布局的优劣。最常用的标准就是使飞线总长度尽可能短。一般来说,飞线总长度越短,意味着布线总长度也是越短(注意:这只是相对于大多数情况是正确的,并不是完全正确);走线越短,走线所占据的印制板面积也就越小,布通率越高。在走线尽可能短的同时,还必须考虑布线密度的问题。如何布局才能使飞线总长度最短并且保证布局密度不至于过高而不能实现是个很复杂的问题。因为,调整布局就是调整封装的放置位置,一个封装的焊盘往往和几个甚至几十个网络同时相关联,减小一个网络飞线长度可能会增长另一个网络的飞线长度。如何能够调整封装的位置到最佳点实在给不出太实用的标准,实际操作时,主要依靠设计者的经验观查屏幕显示的飞线是否简捷、有序和计算出的总长度是否最短。飞线是手工布局和布线的主要参考标准,手工调整布局时尽量使飞线走最短路径,手工布线时常常按照飞线指示的路径连接各个焊盘。Protel的飞线优化算法可以有效地解决飞线连接的最短路径问题。飞线的连接策略Protel提供了两种飞线连接方式供使用者选择:顺序飞线和最短树飞线。在布线参数设置中的飞线模式页可以设置飞线连接策略,应该选择最短树策略。动态飞线在有关飞线显示和控制一节中已经讲到: 执行显示网络飞线、显示封装飞线和显示全部飞线命令之一后飞线显示开关打开,执行隐含全部飞线命令后飞线显示开关关闭。

从IC芯片的发展及封装形式来看,芯片体积越来越小、引脚数越来越多;同时,由于近年来IC工艺的发展,使得其速度也越来越高。这就带来了一个问题,即电子设计的体积减小导致电路的布局布线密度变大,而同时信号的频率还在提高,从而使得如何处理高速信号问题成为一个设计能否成功的关键因素。随着电子系统中逻辑复杂度和时钟频率的迅速提高,信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要。对于低频设计,线迹互连和板层的影响可以不考虑,但当频率超过50 MHz时,互连关系必须考虑,而在*定系统性能时还必须考虑印刷电路板板材的电参数。因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性(Signal Integrity,SI)问题。当硬件工作频率增高后,每一根布线网络上的传输线都可能成为发射天线,对其他电子设备产生电磁辐射或与其他设备相互干扰,从而使硬件时序逻辑产生混乱。电磁兼容性(Electromagnetic Compatibility,EMC)的标准提出了解决硬件实际布线网络可能产生的电磁辐射干扰以及本身抵抗外部电磁干扰的基本要求。1 高速数字电路设计的几个基本概念在高速数字电路中,由于串扰、反射、过冲、振荡、地弹、偏移等信号完整性问题,本来在低速电路中无需考虑的因素在这里就显得格外重要;另外,随着现有电气系统耦合结构越来越复杂,电磁兼容性也变成了一个不能不考虑的问题。要解决高速电路设计的问题,首先需要真正明白高速信号的概念。高速不是就频率的高低来说的,而是由信号的边沿速度决定的,一般认为上升时间小于4倍信号传输延迟时可视为高速信号。即使在工作频率不高的系统中,也会出现信号完整性的问题。这是由于随着集成电路工艺的提高,所用器件I/O端口的信号边沿比以前更陡更快,因此在工作时钟不高的情况下也属于高速器件,随之带来了信号完整性的种种问题。

现在市面上流行的EDA工具软件很多,但除了使用的术语和功能键的位置不一样外都大同小异,如何用这些工具更好地实现PCB的设计呢?在开始布线之前对设计进行认真的分析以及对工具软件进行认真的设置将使设计更加符合要求。下面是一般的设计过程和步骤。1、确定PCB的层数电路板尺寸和布线层数需要在设计初期确定。如果设计要求使用高密度球栅数组(BGA)组件,就必须考虑这些器件布线所需要的最少布线层数。布线层的数量以及层叠(stack-up)方式会直接影响到印制线的布线和阻抗。板的大小有助于确定层叠方式和印制线宽度,实现期望的设计效果。多年来,人们总是认为电路板层数越少成本就越低,但是影响电路板的制造成本还有许多其它因素。近几年来,多层板之间的成本差别已经大大减小。在开始设计时最好采用较多的电路层并使敷铜均匀分布,以避免在设计临近结束时才发现有少量信号不符合已定义的规则以及空间要求,从而被迫添加新层。在设计之前认真的规划将减少布线中很多的麻烦。2、设计规则和限制自动布线工具本身并不知道应该做些什幺。为完成布线任务,布线工具需要在正确的规则和限制条件下工作。不同的信号线有不同的布线要求,要对所有特殊要求的信号线进行分类,不同的设计分类也不一样。每个信号类都应该有优先级,优先级越高,规则也越严格。规则涉及印制线宽度、过孔的最大数量、平行度、信号线之间的相互影响以及层的限制,这些规则对布线工具的性能有很大影响。认真考虑设计要求是成功布线的重要一步。

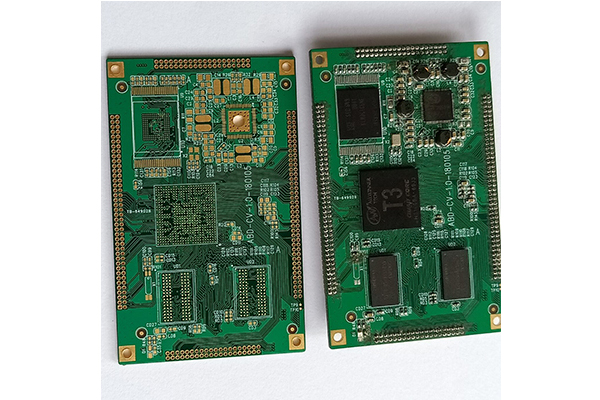

湖南专业贴片SMT线路板打样本身的基板是由隔热、并不易弯曲的材质所制作成。在表层能够看到的很小线路材料是铜箔,贴片SMT加工厂原本铜箔是覆盖在整个线路板板上的,并且在生产过程中部份被蚀刻掉,留下来的就变成网状的细小线路了。这些线路被称作导线或称布线,用来提供线路板上零件的电路连接。通常PCB板的颜色都是棕色或是绿色,这是阻焊漆的颜色。是绝缘的防护层,可以保护铜线,也可以防止零件被焊到错误的地方。现在显卡和主板上都是多层板,很大程度上可以增加布线的面积。多层板用上了更多单或双面的布线板,并在每层板间放进一层绝缘层后压合。PCB板的层数就代表了有几层独立的布线层,通常层数都是偶数,并且包含最外侧的两层,常见的PCB板一般是4~8层的结构。很多PCB板的层数可以通过观看PCB板的切面看出来。但实际上,没有人能有这么好的眼力。所以,下面再教大家一种方法。多层板打样的电路连接是通过埋孔和盲孔技术,主板和显示卡大多使用4层的PCB板,也有些是采用6、8层,甚至10层的PCB板。要想看出是PCB有多少层,通过观察导孔就可以辩识,因为在主板和显示卡上使用的4层板是第1、第4层走线,其他几层另有用途(地线和电源)。所以,同双层板一样,导孔会打穿PCB板。如果有的导孔在PCB板正面出现,却在反面找不到,那么就一定是6/8层板了。如果PCB板的正反面都能找到相同的导孔,自然就是4层板了。把主板对着有光处,看到导孔的位置,如果能透光,这就是8/6层板,否就是四层板.