日常维护与保养方法1、槽体的维护与保养垂直电镀线与水平电镀线的主要区别在于电路板的运送方式不同,而对于槽体的维护及保养方法本质上相差不大。7d要对各水洗槽进行一次清洗对酸洗槽,进行一次清洗并更换其槽液;对槽体内的喷淋装置进行一次检查,查看有无出现阻塞情况,对出现阻塞情况的要及时进行疏通;对镀铜槽、镀锡槽上的导电支座及阳极与火线接触位,进行一次清洁清洁时可用抹布擦拭及砂纸进行打磨;对镀铜槽、镀锡槽的钛篮、锡条篮进行一次检查,更换烂的钛篮袋、锡条篮,并添加铜球、锡条,在7d添加完铜球、锡条后,须对电镀铜槽、电镀锡槽进行电解。7d还要使用高、低电流方式进行试生产,使新添加铜球、锡条完后,生产的性能稳定后再进行生产。每90要对铜球及阳极袋进行一次清洗。每120~150d使用活性碳对槽液进行一次过滤清洁,滤去槽液中的杂质,对锡槽进行一次清洗。2、垂直电镀线振动机构的维护与保养在垂直电镀上,为保证电镀时面铜的均匀性及孔铜的效果,会对板进行振动摇摆,槽体上会有振动摇摆机构。30d要对减速机进行检查,看其是否运转正常,检查其紧固性;要检查震动安装马达螺栓的紧固性;检查震动橡胶的磨损情况,对于磨损比较严重的,要进行及时的更换。180d对接线盒内的电源线接触情形进行检查,对出现接头松动要及时加以紧固,对电线绝缘层熔化或老化的电源线,要及时进行更换电源线,保证电源线之间的绝缘性;要对振动机构上的所有轴承进行一次检查,上一次润滑脂,对严重磨损的轴承要进行及时的更换。3、垂直电镀线行车的维护与保养垂直电镀线是采用行车、挂具对电路板进行传送。每周要对吊车及挂具进行一次清洁(行车及挂具不用拆卸),使其外观保持整洁,清洁时可使用抹布抹洗,并使用砂纸打磨。30d对挂具进行一次检查,查看挂具的破损情况;对行车的电机及减速机进行一次检查和维护,查看其整个传动装置,保证其正常运行。180d对行车及挂具进行一次深入的清洁及保养,要将挂具从行车上拆卸下来进行清洁。

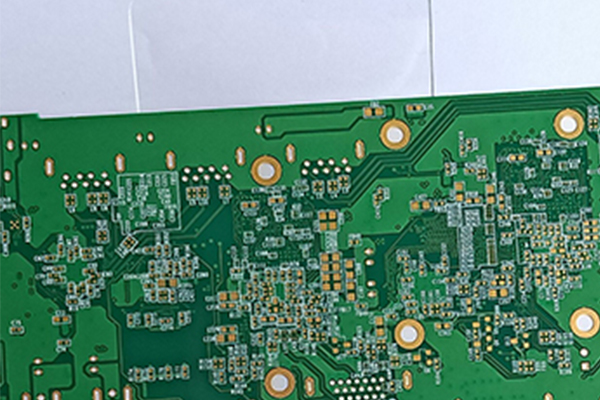

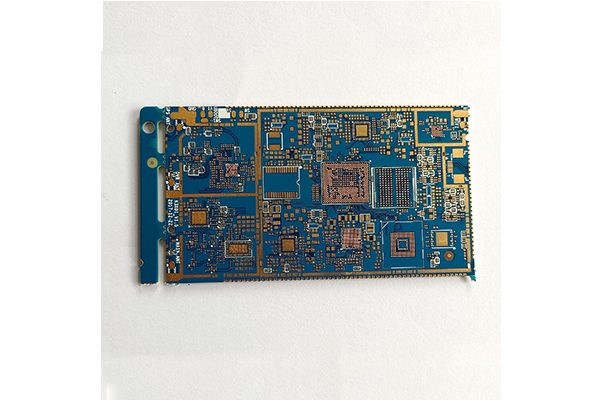

线路板打样本身的基板是由隔热、并不易弯曲的材质所制作成。在表层能够看到的很小线路材料是铜箔,原本铜箔是覆盖在整个线路板板上的,并且在生产过程中部份被蚀刻掉,留下来的就变成网状的细小线路了。这些线路被称作导线或称布线,用来提供线路板上零件的电路连接。通常PCB板的颜色都是棕色或是绿色,这是阻焊漆的颜色。是绝缘的防护层,可以保护铜线,也可以防止零件被焊到错误的地方。现在显卡和主板上都是多层板,很大程度上可以增加布线的面积。多层板用上了更多单或双面的布线板,并在每层板间放进一层绝缘层后压合。PCB板的层数就代表了有几层独立的布线层,通常层数都是偶数,并且包含最外侧的两层,常见的PCB板一般是4~8层的结构。很多PCB板的层数可以通过观看PCB板的切面看出来。但实际上,没有人能有这么好的眼力。所以,下面再教大家一种方法。多层板打样的电路连接是通过埋孔和盲孔技术,主板和显示卡大多使用4层的PCB板,也有些是采用6、8层,甚至10层的PCB板。要想看出是PCB有多少层,通过观察导孔就可以辩识,因为在主板和显示卡上使用的4层板是第1、第4层走线,其他几层另有用途(地线和电源)。所以,同双层板一样,导孔会打穿PCB板。如果有的导孔在PCB板正面出现,却在反面找不到,那么就一定是6/8层板了。如果PCB板的正反面都能找到相同的导孔,自然就是4层板了。把主板对着有光处,看到导孔的位置,如果能透光,这就是8/6层板,否就是四层板.

浙江开发线路板印制1.寄生电容过孔本身存在着对地或电源的寄生电容,如果已知过孔在内层上的隔离孔直径为D2;开发线路板印制过孔焊盘的直径为D1;PCB的厚度为T;板基材的相对介电常数为ε;过孔的寄生电容延Κ了电路中信号的上升时问,降低了电路的速度。如果一块厚度为25mil的PCB,使用内径为10mil,焊盘直径为20mil的过孔,内层电气间隙宽度为32mil时,可以通过上面的公式近似算出过孔的寄生电容大致为0.259 pF。如果走线的特性阻抗为30Ω,则该寄生电容引起的信号上升时间延长量。系数1/2是因为过孔在走线的中途。从这些数值可以看出,尽管单个过孔的寄生电容引起的上升沿变缓的效用不是很明显,但是如果走线中多次使用过孔进行层间的切换,设计者还是要慎重考虑的。2.寄生电感过孔还具有与其高度和直径直接相关的串联寄生电感。若九是过孔的高度;d是中心钻孔的直径;则过孔的寄生电感L近似为在高速数字电路的设计中,寄生电感带来的危害超过寄生电容的影响。过孔的寄生串联电感会削弱旁路电容在电源或地平面滤除噪声的作用,减弱整个电源系统的滤波效用c因此旁路和去耦电容的过孔应该尽可能短,以使其电感值最小。通过上面对过孔寄生特性的分析,为了减小过孔的寄生效应带来的不利影响,在进行高速PCB设计时应尽量做到:· 尽量减少过孔,尤其是时钟信号走线;· 使用较薄的PCB有利于减小过孔的两种寄生参数;· 过孔阻抗应该尽可能与其连接的走线的阻抗相匹配,以便减小信号的反射;

相信对做硬件的工程师,毕业开始进公司时,在设计PCB时,老工程师都会对他说,PCB走线不要走直角,走线一定要短,电容一定要就近摆放等等。但是一开始我们可能都不了解为什么这样做,就凭他们的几句经验对我们来说是远远不够的哦,当然如果你没有注意这些细节问题,今后又犯了,可能又会被他们骂,“都说了多少遍了电容一定要就近摆放,放远了起不到效果等等”,往往经验告诉我们其实那些老工程师也是只有一部分人才真正掌握其中的奥妙,我们一开始不会也不用难过,多看看资料很快就能掌握的。直到被骂好几次后我们回去找相关资料,为什么设计PCB电容要就近摆放呢,等看了资料后就能了解一些,可是网上的资料很杂散,很少能找到一个很全方面讲解的。下面这些内容是我转载的一篇关于电容去耦半径的讲解,相信你看了之后可以很牛x的回答和避免类似问题的发生。老师问: 为什么去耦电容就近摆放呢?学生答: 因为它有有效半径哦,放的远了失效的。电容去耦的一个重要问题是电容的去耦半径。大多数资料中都会提到电容摆放要尽量靠近芯片,多数资料都是从减小回路电感的角度来谈这个摆放距离问题。确实,减小电感是一个重要原因,但是还有一个重要的原因大多数资料都没有提及,那就是电容去耦半径问题。如果电容摆放离芯片过远,超出了它的去耦半径,电容将失去它的去耦的作用。理解去耦半径最好的办法就是考察噪声源和电容补偿电流之间的相位关系。当芯片对电流的需求发生变化时,会在电源平面的一个很小的局部区域内产生电压扰动,电容要补偿这一电流(或电压),就必须先感知到这个电压扰动。信号在介质中传播需要一定的时间,因此从发生局部电压扰动到电容感知到这一扰动之间有一个时间延迟。同样,电容的补偿电流到达扰动区也需要一个延迟。因此必然造成噪声源和电容补偿电流之间的相位上的不一致。

随着集成电路输出开关速度提高以及PCB板密度增加,信号完整性已经成为高速数字PCB设计必须关心的问题之一。元器件和PCB板的参数、元器件在PCB板上的布局、高速信号的布线等因素,都会引起信号完整性问题,导致系统工作不稳定,甚至完全不工作。如何在PCB板的设计过程中充分考虑到信号完整性的因素,并采取有效的控制措施,已经成为当今PCB设计业界中的一个热门课题。基于信号完整性计算机分析的高速数字PCB板设计方法能有效地实现PCB设计的信号完整性。1. 信号完整性问题概述信号完整性(SI)是指信号在电路中以正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题主要表现为5个方面:延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)。延迟是指信号在PCB板的导线上以有限的速度传输,信号从发送端发出到达接收端,其间存在一个传输延迟。信号的延迟会对系统的时序产生影响,在高速数字系统中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。另外,当PCB板上导线(高速数字系统中称为传输线)的特征阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使信号波形发生畸变,甚至出现信号的过冲和下冲。信号如果在传输线上来回反射,就会产生振铃和环绕振荡。