1. 如果是人工焊接,要养成好的习惯,首先,焊接前要目视检查一遍PCB板,并用万用表检查关键电路(特别是电源与地)是否短路;其次,每次焊接完一个芯片就用万用表测一下电源和地是否短路;此外,焊接时不要乱甩烙铁,如果把焊锡甩到芯片的焊脚上(特别是表贴元件),就不容易查到。2. 在计算机上打开PCB图,点亮短路的网络,看什么地方离的最近,最容易被连到一块。特别要注意IC内部短路。3. 发现有短路现象。拿一块板来割线(特别适合单/双层板),割线后将每部分功能块分别通电,一部分一部分排除。4. 使用短路定位分析仪,如:新加坡PROTEQ CB2000短路追踪仪,香港灵智科技QT50短路追踪仪,英国POLAR ToneOhm950多层板路短路探测仪等等。5. 如果有BGA芯片,由于所有焊点被芯片覆盖看不见,而且又是多层板(4层以上),因此最好在设计时将每个芯片的电源分割开,用磁珠或0欧电阻连接,这样出现电源与地短路时,断开磁珠检测,很容易定位到某一芯片。由于BGA的焊接难度大,如果不是机器自动焊接,稍不注意就会把相邻的电源与地两个焊球短路。

在PCB(印制电路板)中,印制导线用来实现电路元件和器件之间电气连接,是PCB中的重要组件,PCB导线多为铜线,铜自身的物理特性也导致其在导电过程中必然存在一定的阻抗,导线中的电感成分会影响电压信号的传输,而电阻成分则会影响电流信号的传输,在高频线路中电感的影响尤为严重,因此,在PCB设计中必须注意和消除印制导线阻抗所带来的影响。1印制导线产生干扰的原因PCB上的印制导线通电后在直流或交流状态下分别对电流呈现电阻或感抗,而平行导线之间存在电感效应,电阻效应,电导效应,互感效应;一根导线上的变化电流必然影响另一根导线,从而产生干扰;PCB板外连接导线甚至元器件引线都可能成为发射或接收干扰信号的天线。印制导线的直流电阻和交流阻抗可以通过公式和公式来计算,R=PL/S和XL=2πfL式中L为印制导线长度(m),s为导线截面积(mm2),ρ为铜的电阻率,TT为常数,f为交流频率。正是由于这些阻抗的存在,从而产生一定的电位差,这些电位差的存在,必然会带来干扰,从而影响电路的正常工作。2 PCB电流与导线宽度的关系PCB导线宽度与电路电流承载值有关,一般导线越宽,承载电流的能力越强。在实际的PCB制作过程中,导线宽度应以能满足电气性能要求而又便于生产为宜,它的最小值以承受的电流大小而定,导线宽度和间距可取0.3mm(12mil)。导线的宽度在大电流的情况下还要考虑其温升问题。PCB设计铜铂厚度、线宽

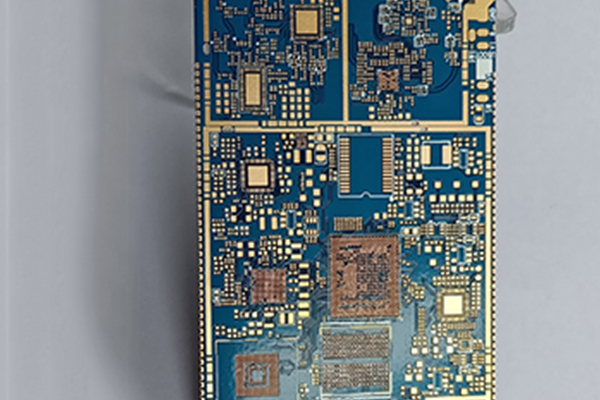

一、PCB沉金采用的是化学沉积的方法,通过化学氧化还原反应的方法生成一层镀层,一般厚度较厚,是化学镍金金层沉积方法的一种,可以达到较厚的金层。二、PCB镀金采用的是电解的原理,也叫电镀方式。其他金属表面处理也多数采用的是电镀方式。在实际产品应用中,90%的金板是沉金板,因为镀金板焊接性差是他的致命缺点,也是导致很多公司放弃镀金工艺的直接原因!沉金工艺在印制线路表面上沉积颜色稳定,光亮度好,镀层平整,可焊性良好的镍金镀层。基本可分为四个阶段:前处理(除油,微蚀,活化、后浸),沉镍,沉金,后处理(废金水洗,DI水洗,烘干)。沉金厚度在0.025-0.1um间。金应用于电路板表面处理,因为金的导电性强,抗氧化性好,寿命长,而镀金板与沉金板最根本的区别在于,镀金是硬金(耐磨),沉金是软金(不耐磨)。1、沉金与镀金所形成的晶体结构不一样,沉金对于金的厚度比镀金要厚很多,沉金会呈金黄色,较镀金来说更黄(这是区分镀金和沉金的方法之一),镀金的会稍微发白(镍的颜色)。2、沉金与镀金所形成的晶体结构不一样,沉金相对镀金来说更容易焊接,不会造成焊接不良。沉金板的应力更易控制,对有邦定的产品而言,更有利于邦定的加工。同时也正因为沉金比镀金软,所以沉金板做金手指不耐磨(沉金板的缺点)。3、PCB沉金板只有焊盘上有镍金,趋肤效应中信号的传输是在铜层不会对信号有影响。4、沉金较镀金来说晶体结构更致密,不易产成氧化。5、随着电路板加工精度要求越来越高,线宽、间距已经到了0.1mm以下。镀金则容易产生金丝短路。沉金板只有焊盘上有镍金,所以不容易产成金丝短路。6、沉金板只有焊盘上有镍金,所以线路上的阻焊与铜层的结合更牢固。工程在作补偿时不会对间距产生影响。7、对于要求较高的板子,平整度要求要好,一般就采用沉金,沉金一般不会出现组装后的黑垫现象。沉金板的平整性与使用寿命较镀金板要好。所以目前大多数工厂都采用了沉金工艺生产金板。但是沉金工艺比镀金工艺成本更贵(含金量更高),所以依然还有大量的低价产品使用镀金工艺。

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响.因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:1、阻抗匹配2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇行线就是为了适应PCI33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.

四川线路板印制随着集成电路输出开关速度提高以及PCB板密度增加,信号完整性已经成为高速数字PCB设计必须关心的问题之一。专业线路板印制元器件和PCB板的参数、元器件在PCB板上的布局、高速信号的布线等因素,都会引起信号完整性问题,导致系统工作不稳定,甚至完全不工作。如何在PCB板的设计过程中充分考虑到信号完整性的因素,并采取有效的控制措施,已经成为当今PCB设计业界中的一个热门课题。基于信号完整性计算机分析的高速数字PCB板设计方法能有效地实现PCB设计的信号完整性。1. 信号完整性问题概述信号完整性(SI)是指信号在电路中以正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题主要表现为5个方面:延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)。延迟是指信号在PCB板的导线上以有限的速度传输,信号从发送端发出到达接收端,其间存在一个传输延迟。信号的延迟会对系统的时序产生影响,在高速数字系统中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。另外,当PCB板上导线(高速数字系统中称为传输线)的特征阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使信号波形发生畸变,甚至出现信号的过冲和下冲。信号如果在传输线上来回反射,就会产生振铃和环绕振荡。

高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性(延迟差超过一个时钟周期时会错读下一周期的数据),一般要求延迟差不超过1/4时钟周期,单位长度的线延迟差也是固定的,延迟跟线宽,线长,铜厚,板层结构有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越易受分布电容和分布电感的影响.因为应用场合不同具不同的作用,如果蛇形走线在电脑板中出现,其主要起到一个滤波电感的作用,提高电路的抗干扰能力,电脑主机板中的蛇形走线,主要用在一些时钟信号中,如CIClk,AGPClk,它的作用有两点:1、阻抗匹配 2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是解决办法。一般来讲,蛇形走线的线距>=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等.